处理器体系结构

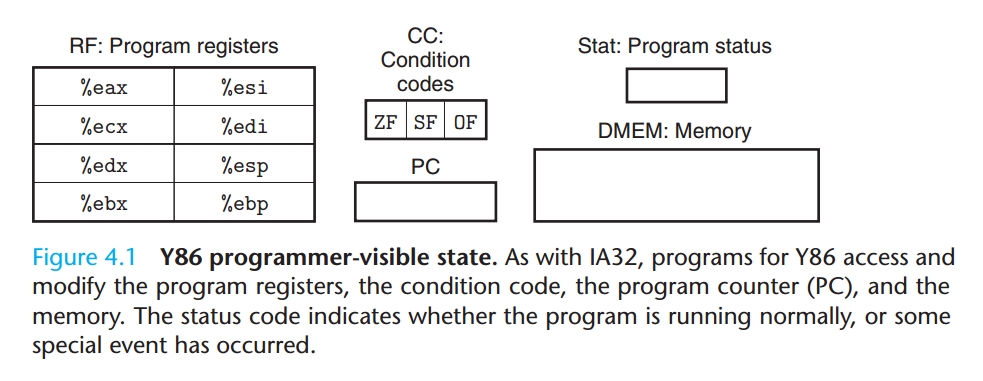

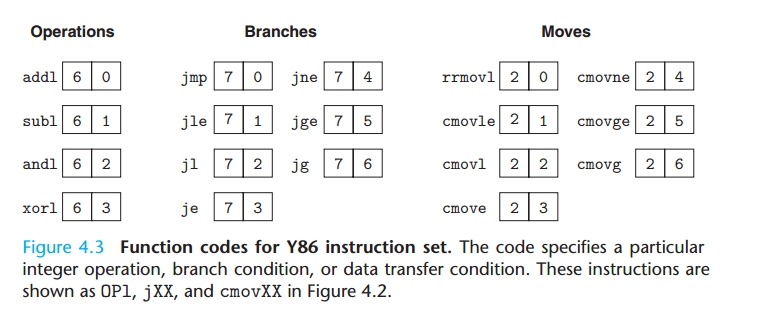

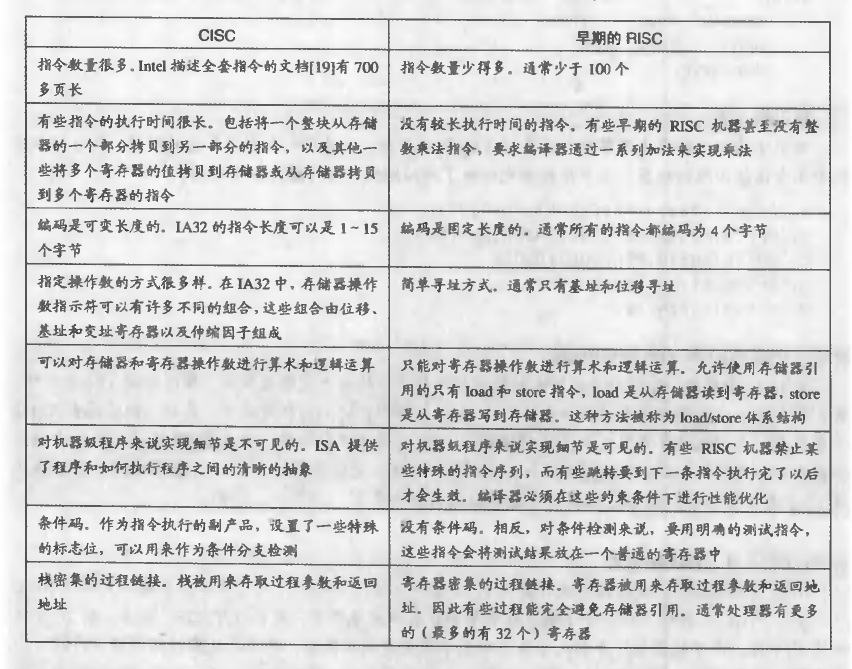

Y86指令集体系结构

逻辑设计和硬件控制语言HCL

逻辑门

组合电路和HCL布尔表达式

字级的组合电路和HCL整数表达式

集合关系(set membership)

存储器和时钟控制

Y86的顺序(sequential)实现

将处理组织成阶段

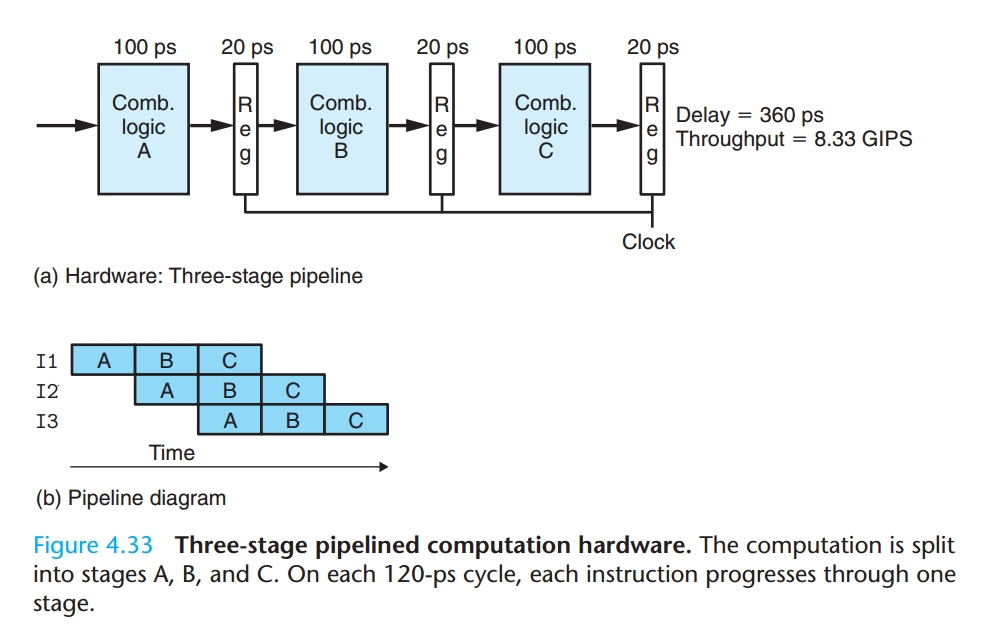

流水线的通用原理

计算流水线

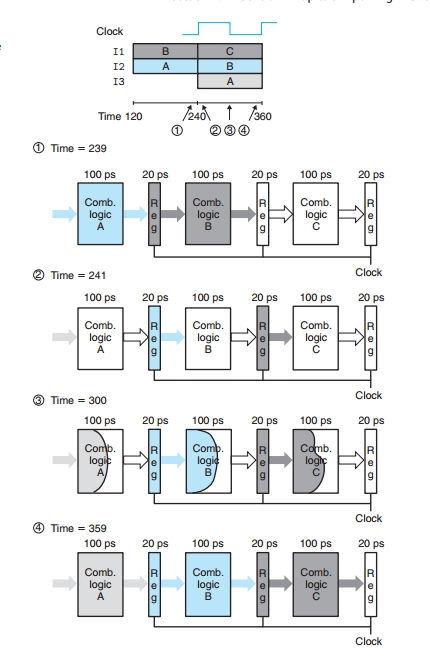

流水线操作的详细说明

流水线的局限性

带反馈的流水线系统

Y86的流水线实现

插入流水线寄存器

对信号做重新排列和标号

预测下一个PC

流水先冒险(hazard)

用暂停(stalling)来避免数据冒险

用转发(forwarding)来避免数据冒险

小结

最后更新于